top of page

Tabulation of PLL Design Values

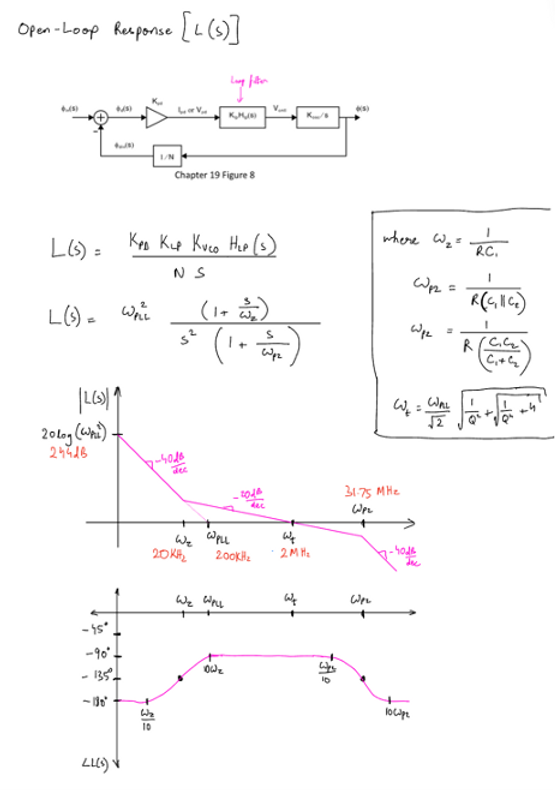

Type-II PLL Open Loop Response (Hand Analysis)

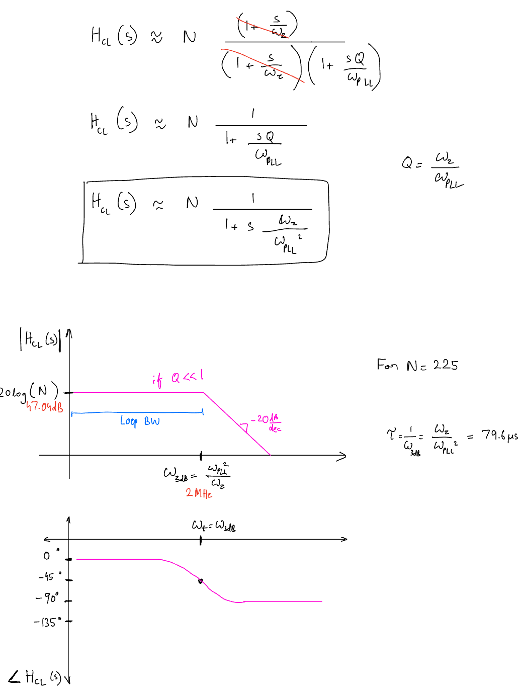

Type-II Closed Loop Response (Hand Analysis)

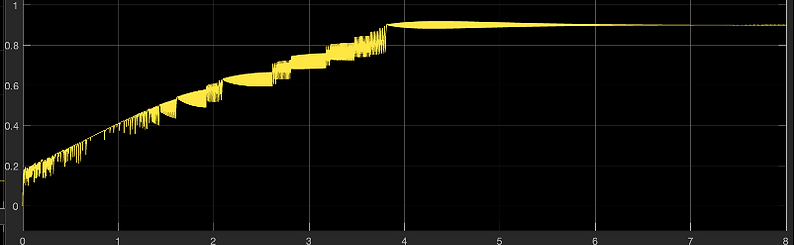

PLL Locking Simulation (VCO Control Voltage vs Time)

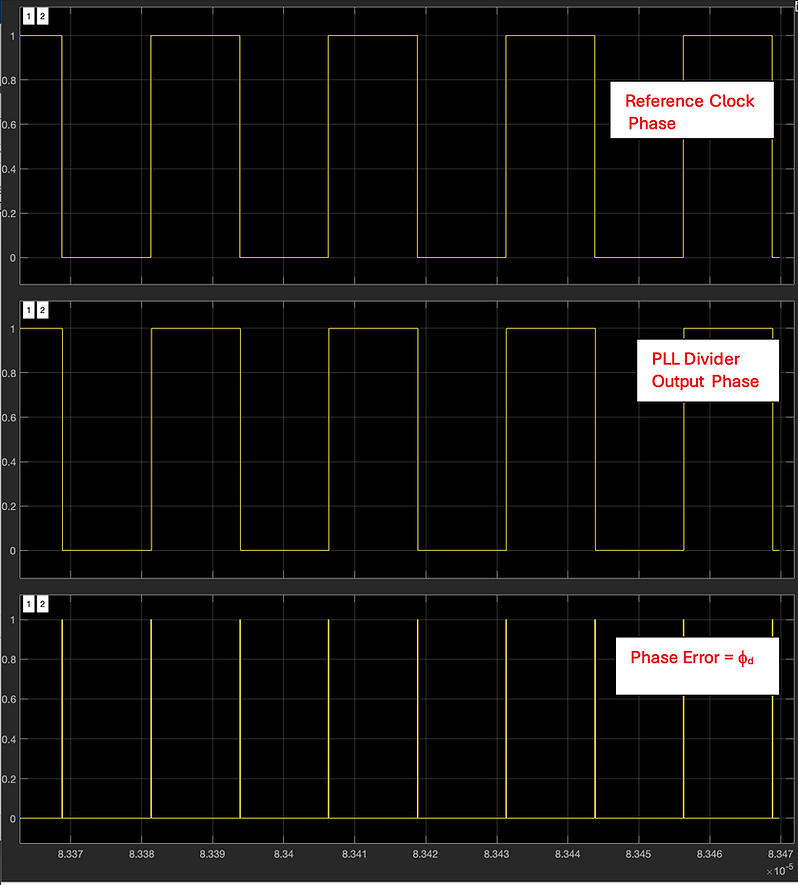

PFD "UP" Output Before Lock (Top) And After Lock (Below)

Charge Pump Output Before Lock (Top) And After Lock (Below)

VCO Control Voltage Before Lock (Top) And After Lock (Below)

PLL Re-Locking Simulation (REF freq changed by +0.1%)

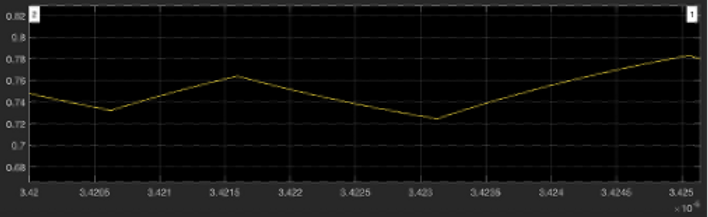

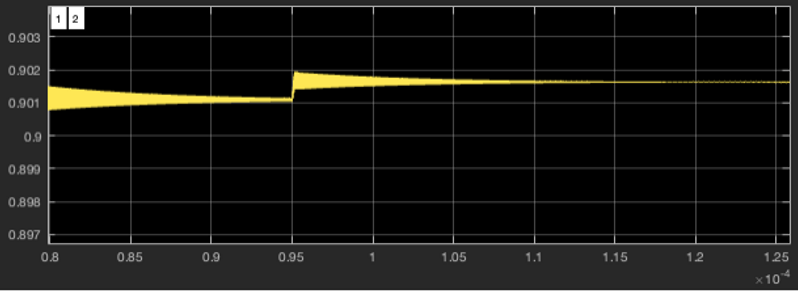

Static Phase Error After Lock

bottom of page