top of page

AC Gain and Phase (TT corner)

AC Gain and Phase (FF corner)

AC Gain and Phase (SS corner)

Voltage Error @ 1MHz (TT Corner)

Voltage Error @ 1MHz (FF Corner)

Voltage Error @ 1MHz (SS Corner)

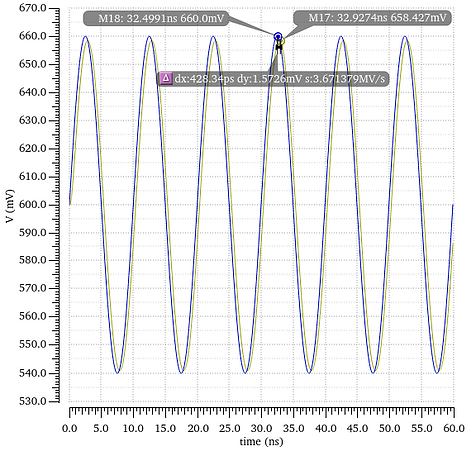

Voltage Error @ 100MHz (TT Corner)

Voltage Error @ 100MHz (FF Corner)

Voltage Error @ 100MHz (SS Corner)

Current Mirror Op-Amp Noise Hand Analysis

Input-Referred Noise

Noise Summary @ 1KHz

Noise Summary @ 100MHz

Project Documentation (button below) includes:

1. Current Mirror Op-Amp Schematics with DC Operating Points, Component Parameters

2. Detailed Design Procedure

3. AC Gain and Phase across TT,FF,SS corner

4. Voltage Error across TT,FF,SS corner

5. Hand-analysis of Noise at 1KHz, 100MHz

6. Cadence Noise Analysis at 1KHz, 100MHz

bottom of page